FPGA系统能力贯通实验平台

核心功能

贯通式培养

· 实现一个RISC-V流水线CPU(支持SoC)

· 实现一个RISC-V操作系统内核

· 实现一个RISC-V编译器

· 要求CPU可以运行在FPGA开发板上

· 要求操作系统内核可以运行在CPU上

· 要求高级语言代码经编译器编译后生成的二进制程序可以运行在CPU上

· 编译后的二进制程序可以被操作系统内核进行多任务调度和管理(进程+虚存)

在线运行

支持学生在线申请 FPGA 硬件开发板,支持自动为学生自动分配空闲开发板。在开发板资源不够时,支持排队进入在线实验环境。

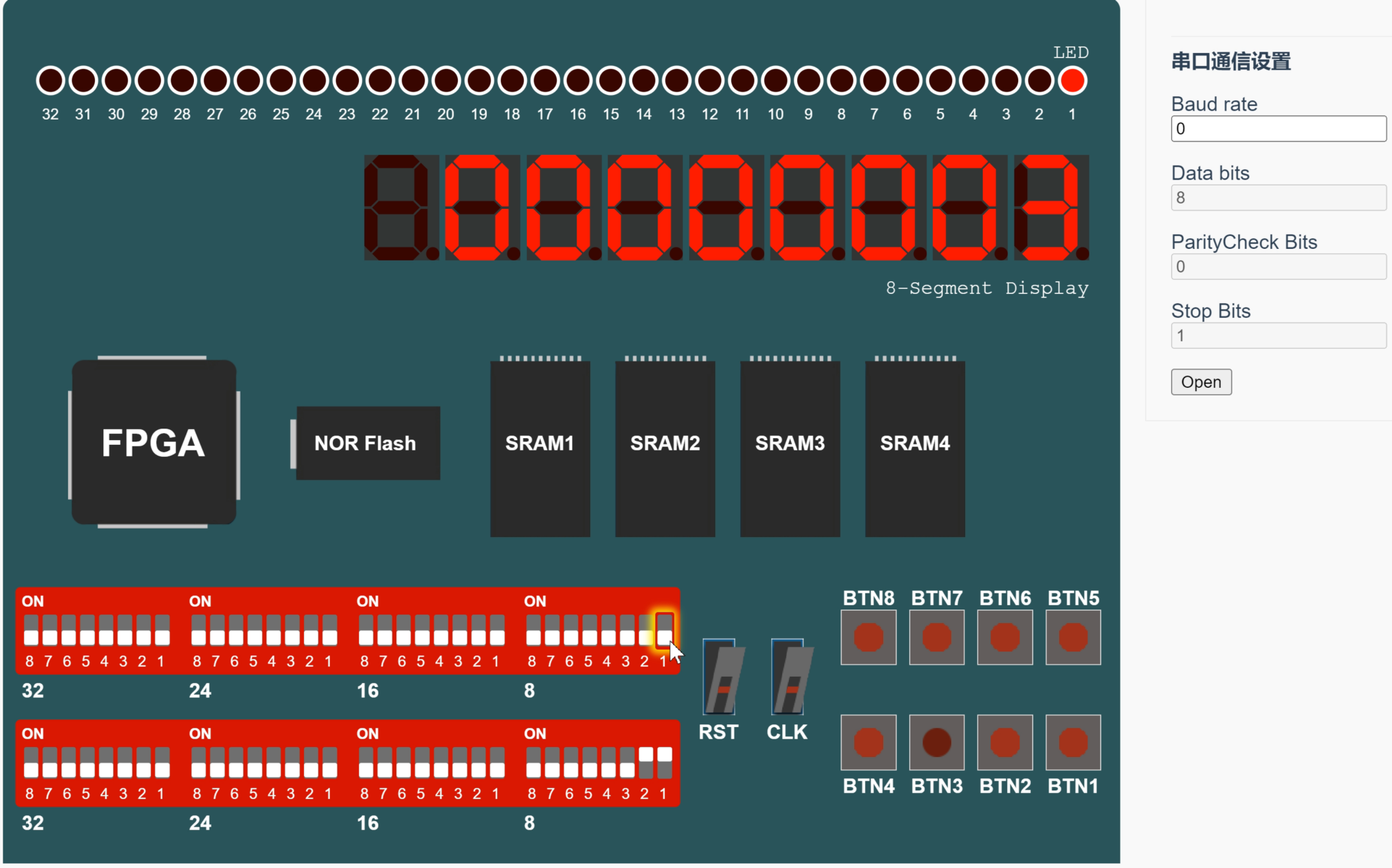

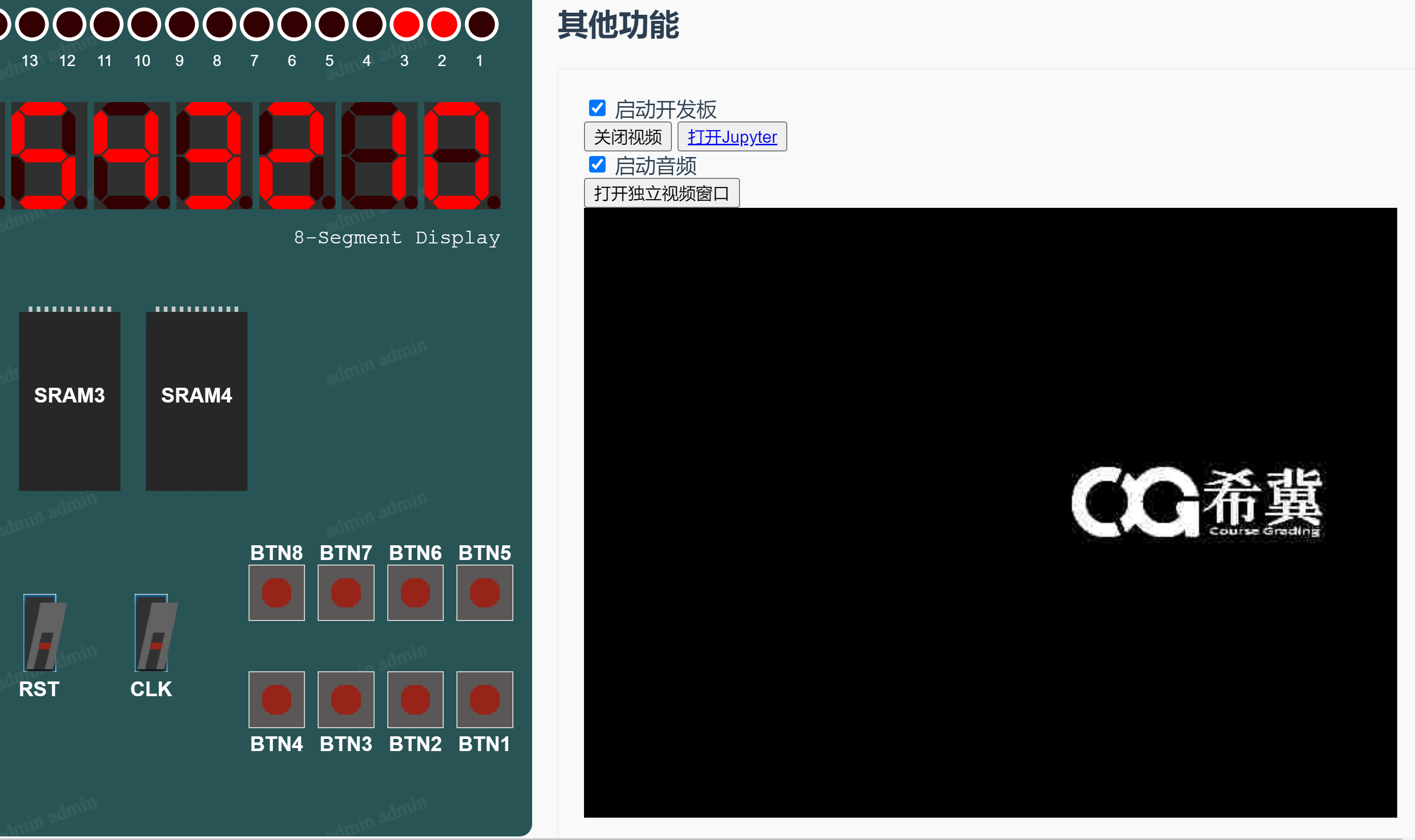

实验平台为每个学生分配一个由 FPGA 硬件开发板驱动的FPGA电路运行面板。通过运行面板,学生可看到电路的实时运行效果;通过输入外设,实现与 FPGA 上运行的电路进行实时交互。

随时随地

学生通过浏览器即可随时随地登录实验平台开始实验。点击“开始实验”后,进入 FPGA 电路运行面板实验环境。在电路运行面板上,学生可在线申请 FPGA 硬件开发板。

支持学生在线烧录位流到远程 FPGA 硬件开发板上运行,摆脱时间和空间限制。学生可在图书馆、自习室、宿舍等非机房环境中开展硬件实验。

当开发板出现异常时,支持学生一键远程重启开发板或切换新开发板。

外设丰富

提供丰富的输入/输出外设,支持外设数量与种类的可持续扩展,不受 FPGA 芯片引脚数量约束。当前外设包括:

· LED 灯:32 个

· LED 点阵:16*16,4 个

· 7 段数码管(带小数点位):9 个

· 拨码开关:32 个/组,共 2 组

· 按键:8 个

· 复位键:1 个

· 时钟键:1 个

· 音频输出:支持

· 视频输出:支持,HDMI/VGA

· 串口:支持

自动评测

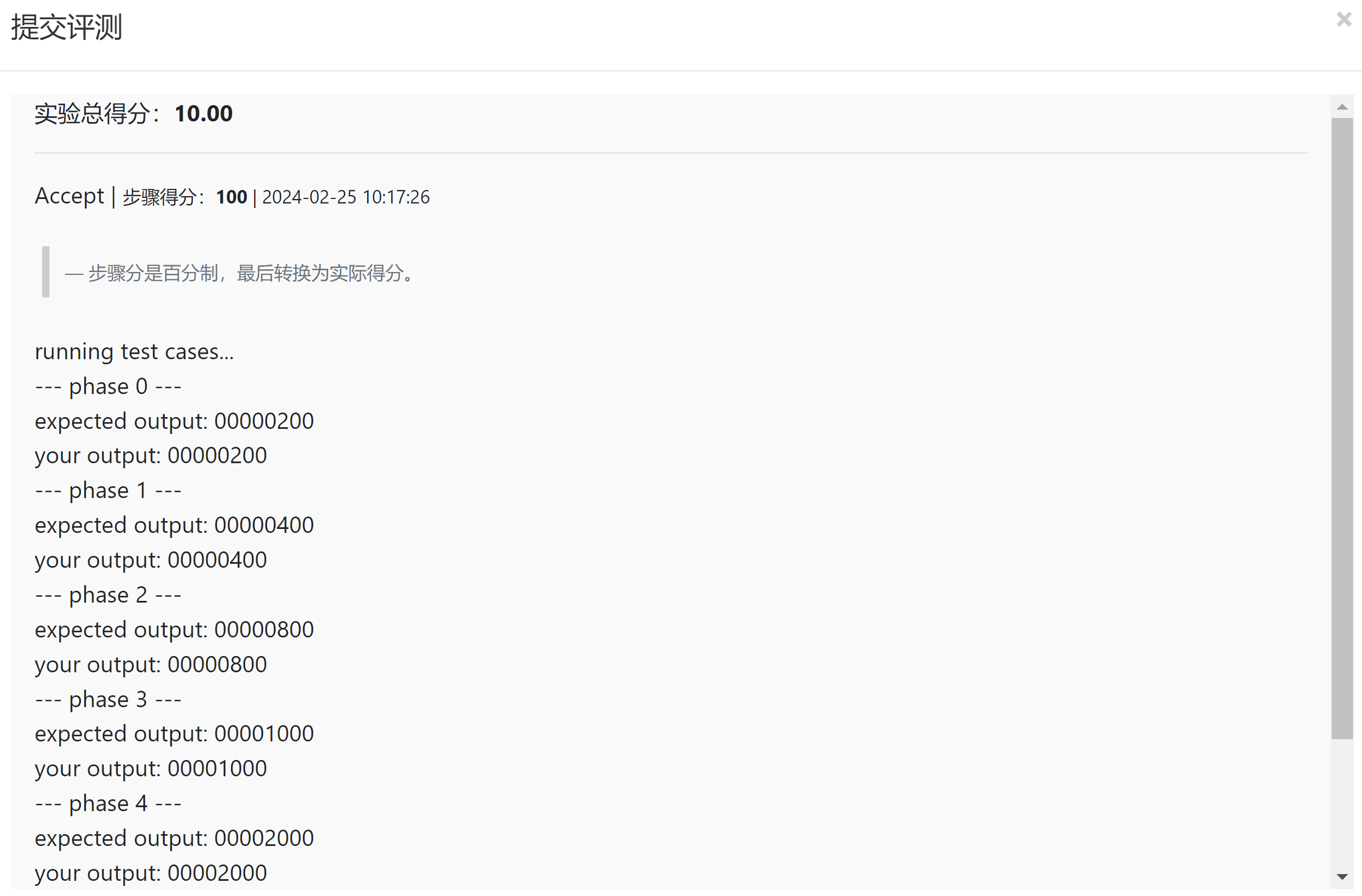

学生提交位流、镜像、程序文件后,平台可自动在远程FPGA硬件开发板上运行学生的CPU电路、OS镜像、程序,评测学生所提交CPU、OS、程序的功能是否正确,性能是否满足要求。根据评测结果,自动为学生所设计的CPU、OS、编译器进行客观判分。

· 支持基于“VSCode+GDB+OpenOCD+JTAG”的远程代码调试。

· 支持基于“XVC+逻辑分析仪”的远程硬件电路调试。

除了FPGA硬件开发板评测外,实验平台也支持仿真器评测。通过闯关方式将仿真器评测和FPGA开发板评测按实验难度递进顺序自然结合,降低学生开发复杂数字系统(如流水线CPU)的调试难度,增强学生完成实验的信心,提高学生开展实验的兴趣。

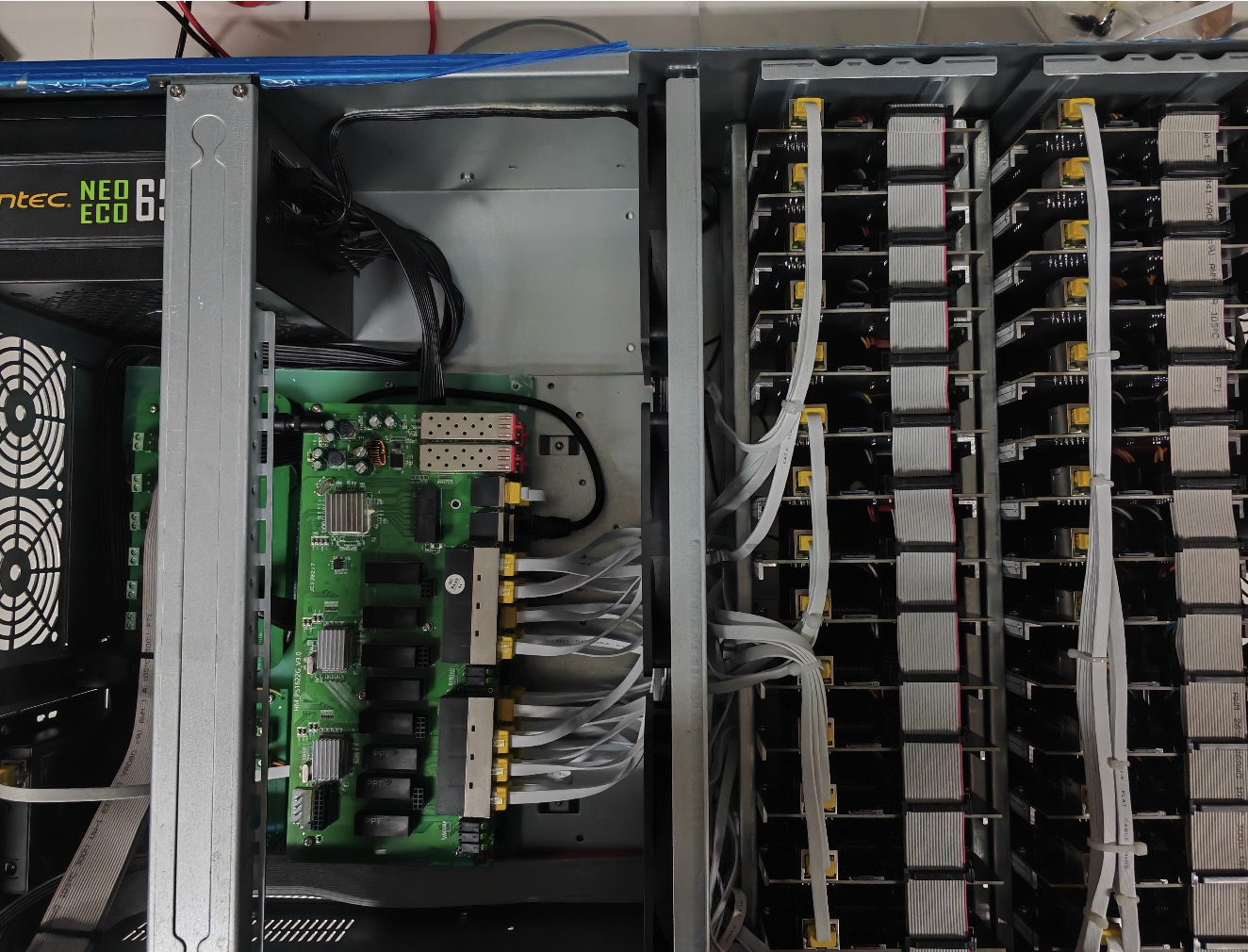

高密度(标配版)

通过将FPGA硬件开发板高密度封装于FPGA服务器中,有效避免传统FPGA开发板或者实验箱在使用过程中的损耗问题。FPGA服务器具有如下特点:

· 自研PCB电路板,采用 4U 标准机箱外壳。

· 每块开发板支持单独插拔,即插即用。

· 服务器通网通电后,可全年 7*24 小时运行。

· 每台服务器中包含 28 块 FPGA 硬件开发板。

· 支持本地交付,多台服务器可组成 FPGA 集群。

· FPGA 型号:XC7Z020,85k LCs,53.2k LUTs

· QSPI NOR FLASH:≥16MB

· Ethernet:1 路

· DDR3 RAM:1GB

· SRAM:2片,64Mbit,SPI 和 QPI 四线读写

· ARM硬核:2 个,主频766MHz,支持音视频硬件加速

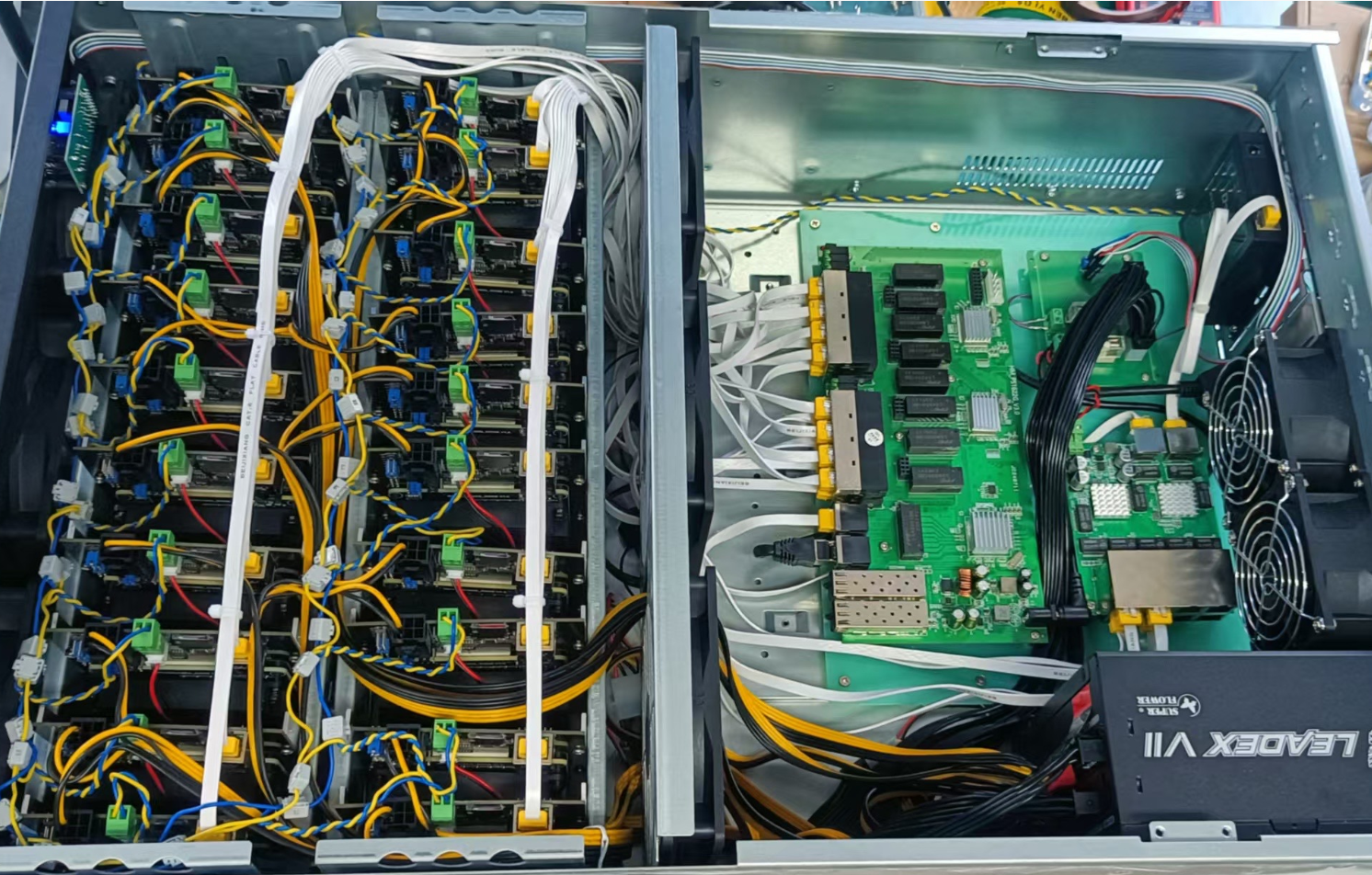

高密度(高配版)

通过将FPGA硬件开发板高密度封装于FPGA服务器中,有效避免传统FPGA开发板或者实验箱在使用过程中的损耗问题。FPGA服务器具有如下特点:

· 自研PCB电路板,采用 4U 标准机箱外壳。

· 每块开发板支持单独插拔,即插即用。

· 服务器通网通电后,可全年 7*24 小时运行。

· 每台服务器中包含 20 块 FPGA 硬件开发板。

· 支持本地交付,多台服务器可组成 FPGA 集群。

· FPGA型号:XCZU15EG,747k LCs,341.04k LUTs

· NAND FLASH:≥64MB

· Ethernet:1 路

· EMMC存储芯片:不低于8GB

· SRAM:2片,64Mbit,SPI和QPI四线读写

· RAM:≥4GB DDR4(PS侧),≥2GB DDR4(PL侧)

· ARM硬核:2个,最高主频≥1.5GHz,支持音视频硬件加速

全栈贯通实验体系

RISC-V CPU设计核心实验 、RISC-V OS内核设计核心实验 、 RISC-V 编译器设计

| RISC-V CPU设计核心实验 | RISC-V OS内核设计核心实验 | RISC-V 编译器设计 |

|---|---|---|

|

实验01:实现寄存器堆 实验02:实现译码和控制单元 实验03:译码阶段基本实现 实验04:执行阶段基本实现 实验05:取址跳转模块基本实现 实验06:存储模块基本实现 实验07:流水线寄存器基本实现 实验08:前递模块基本实现 实验09:分支预测模块和IF阶段基本实现 实验10:完整流水线CPU实现 实验11:RV处理器中断与特权实现 实验12:RV处理器总线与外设模式 实验13:RV处理器OS运行验证 |

实验01:编译与链接(基于RISC-V ISA) 实验02:RISC-V汇编语言编程 实验03:启动(bootstrap) 实验04:串口输出 实验05:内存管理 实验06:上下文切换 实验07:进程调度 实验08:陷阱 实验09:中断 实验10:硬件定时器 实验11:抢占式调度 实验12:锁 实验13:软件定时器 实验14:系统调用 |

实验1:语言解析器 实验2:IR 自动生成 实验3:LA64 代码生成 实验4:转化为 SSA IR 实验5:机器无关优化 实验6:寄存器分配 |

CPU设计入门实验体系

单周期CPU设计 、 流水线CPU设计

| 单周期CPU设计 | 流水线CPU设计 | |

|---|---|---|

|

取指单元设计与实现 寄存器堆设计与实现 ALU算术逻辑单元设计与实现 DataMem数据存储设计与实现 控制器设计与实现 ALU控制器设计与实现 CPU顶层设计与实现 CPU上板验证:控制LED闪烁 CPU上板验证:控制数码管显示数字 CPU上板验证:计算斐波那契数列 |

实现寄存器堆 取指级基本实现 取指-译码中间级实现 译码级基本实现 执行级基本实现 访存级基本实现 写回级基本实现 解决寄存器读写冲突 取指级支持分支 译码级支持分支 译码级访存实现 执行级访存实现 访存级完整实现 写回级完整实现 取指级支持暂停 译码级冲突检测 |

执行级冲突检测 访存级冲突检测 解决访存冲突 实现流水线控制器 CPU上板验证:控制LED闪烁 CPU上板验证:控制数码管显示数字 CPU上板验证:计算斐波那契数列 CPU上板验证:实现秒表计数 CPU上板验证:输出三色图像 CPU上板验证:控制挡板左右移动 CPU上板验证:实现小球反弹动画 CPU上板验证:实现挡板接小球游戏 |

FPGA 入门实验体系

FPGA 快速入门

覆盖LED灯、LED点阵、数码管、拨码开关、复位键、按键、串口、音频、视频等外设。每个实验提供了详细的实验指导手册,可指导学生如何从零开始在FPGA在线实验平台完成所有实验内容。

-

实验1:LED跑马灯实验

下载比特流文件后,即可看到使用32个LED灯实现的跑马灯效果。

-

实验2:LED灯开关实验

下载比特流文件后,拨动某个拨码开关后,对应LED灯亮;拨回后,对应LED灯灭。

-

实验3:4位加法器实验

下载比特流文件后,拨动拨码开关输入2个4位操作数,即可在数码管上显示经过加法器运算之后得到的计算结果。

-

实验4:数码管计数实验

下载比特流文件后,所有数码管按每秒变化1次的频率从000000000计数到FFFFFFFFF。当计数达到FFFFFFFFF后,下次重新从000000000开始计数。计数过程中,小数点位全部点亮。

-

实验5:数码管秒表计数实验

下载比特流文件后,数码管以“时.分.秒.毫秒”格式开始计数。时间位宽格式为:hh.mm.ss.xxx,计数过程中,时、分、秒后的小数点位全部点亮。

-

实验6:LED点阵汉字显示实验

下载比特流文件后,在4个16*16的LED点阵上滚动显示一排汉字,内容为:计算机系统能力培养。

-

实验7:串口读写

下载比特流文件后,可以使用串口发送字符串,在接收端可以看到发送的字符串内容,支持ASCII模式。

-

实验8:蜂鸣器实现7个音调

下载比特流文件后,可以使用7个按键实现7个音调(do、re、mi、fa、sol、la、si)。

-

实验9:蜂鸣器演奏生日快乐

下载比特流后,可以播放使用蜂鸣器演奏的生日快乐伴奏。

-

实验10:VGA显示屏保动画

下载比特流后,可以显示屏保动画。在屏保动画中,Logo标志在黑色背景屏幕内来回移动,碰到屏幕边缘会反弹,每次碰撞时播放提示音,反弹后的Logo切换一次颜色。

数字逻辑实验体系

数字逻辑

| 门电路 | 组合逻辑 | 时序逻辑 | |||

|---|---|---|---|---|---|

|

输出0 输出32位0 1位输入输出 32位输入输出 与门 非门 或门 或非门 与非门 异或门 同或门 32位与门 32位非门 32位或门 32位或非门 32位与非门 |

32位异或门 32位同或门 两位相等 32位相等 两数相等 两数相等(全亮版) |

奇偶校验 所有位做逻辑运算 vector反转 4字节颠倒顺序 实现7458模块 3-8译码器 8-3编码器 优先编码器 4选1数据选择器 4位数值比较器 2选1多路选择器 6选1多路选择器 简单编码器 2选1多路选择器 2选1总线 9选1多路选择器 |

半加器 全加器 4个数求最小(三目运算) 计算3位vector中1的个数 根据原理图实现电路1 根据原理图实现电路2 根据原理图实现电路3 根据表达式实现电路1 根据波形图实现电路1 根据波形图实现电路2 根据波形图实现电路3 根据波形图实现电路4 根据波形图实现电路5 根据波形图实现电路6 |

D触发器 D触发器组合 异步复位触发器 同步复位触发器 同步复位触发器组 同步复位特殊值触发器组 可异步复位的触发器组 带控制端的触发器组 D锁存器 门控触发器 根据真值表实现电路 根据波形图实现电路1 根据波形图实现电路2 上升沿检测 移位寄存器(1位) 移位寄存器(8位) |

算数左右移 双向移位寄存器 四位二进制加减计数器 十进制加减计数器 分频器 |

| 状态机 | LED外设实验 | 数码管外设 | 综合设计 | |

|---|---|---|---|---|

|

验证1000序列(Moore) 验证1000序列(Mealy) 验证1101序列(Mealy) 验证1101序列(Moore) 序列识别 旅鼠1 旅鼠2 旅鼠3 旅鼠4 异步复位Moore状态机 同步复位Moore状态机 根据状态转换表实现状态机1 根据状态转换表实现状态机2 |

LED1闪烁 LED1可控闪烁 LED全闪烁 LED可控全闪烁 LED可控可数闪烁 LED1-8跑马灯 LED1-8可控跑马灯 LED1-8可控可数跑马灯 LED1-8可控往返跑马灯 LED13-20可控双向跑马灯 LED13-20可控双向往返跑马灯 LED低4高4可控跑马灯 LED低4高4可控往返跑马灯 LED无符号数值比较器 LED有符号数值比较器 |

数码管显示1个数 数码管显示8个数 数码管选择显示8数 数码管显示十进制无符号数 数码管显示十进制有符号数 数码管无符号数值比较器 数码管有符号数值比较器 数码管十进制无符号数值比较器 数码管十进制有符号数值比较器 数码管8个数选最大 数码管8个数选最小 数码管8个数选最多 数码管8个数选最少 数码管8个数求平均 数码管8个数升序排序 |

数码管8个数降序排序 数码管8个数动态升序排序 数码管8个数动态降序排序 |

计数器 格雷码计数器 字符自动机(正则表达式匹配) 表达式状态机(表达式校验) 表达式状态机-允许括号(表达式校验) 自动售货机 出租车计费 LED点阵螺旋曲线 控制屏幕画面移动 挡板接小球游戏 |

应用场景

· 基于FPGA系统能力贯通实验平台,可支撑以下课程实验环节的开展:

|

计算机组成原理 编译原理 计算机体系结构 数字电路 FPGA数字系统技术 |

操作系统 数字逻辑 计算机系统基础 数字系统设计 数字集成电路设计 |

· FPGA在线实验可与线下的硬件开发板或实验箱形成互补,学生使用线下硬件开发板或实验箱开发和测试电路,提交到线上FPGA在线实验平台完成考核。